소개

Prof. 박종선

Tel: 02-3290-4827

E-mail: jongsun@korea.ac.kr

- About Professor

- Publication

- Research

- Teaching

- Lab Members

Profile

Professor Jongsun Park

Professor, School of Electrical Engineering, Korea University

Room #716B, Innovation Hall (창의관), Seoul Science Campus, Korea Univ.

Jongsun Park received the B.S. degree in electronics engineering from Korea University, Seoul, Korea, in 1998 and the M.S. and Ph.D. degrees in electrical and computer engineering from Purdue University, West Lafayette, IN, in 2000 and 2005, respectively. He joined the Electrical Engineering faculty of the Korea University, Seoul, Korea, in 2008. From 2005 to 2008, he was with the Signal Processing Technology Group, Marvell Semiconductor Inc., Santa Clara, CA. He was also with the Digital Radio Processor System Design Group, Texas Instruments, Dallas, TX, in Summer of 2002. His research interests focus on variation-tolerant, low-power and high-performance VLSI architectures and circuit designs for digital signal processing and digital communications.

Contact

E-mail)

jongsun

Tel)

+82-2-3290-4827

Education

Ph.D. in Electrical and Computer Engineering, Purdue University, West Lafayette, IN, USA, 2005M.S. in Electrical and Computer Engineering, Purdue University, West Lafayette, IN, USA, 2000B.S. in Electronics Engineering, Korea University, Seoul, Korea, 1998Experience

2008~Present Assistant/Associate/Full Professor, School of Electrical Engineering, Korea University, Seoul, Korea2005~2008 Staff Design Engineer, Marvell Semiconductors, Santa Clara, CA, United States2002 Graduate technical intern, Texas Instruments, TX, United States1999~2005 Research Assistant, Nano-electronics Research Lab., Purdue University, IN, United StatesPublication

Selected Journal Publications

■ Yong-Seok Lim, Woong Choi, Yongju Park, Sangwook Oh, Younghun Kim, and Jongsun Park, "A Novel One-Body Dual Laser Profile based Vibration Compensation in 3D Scanning Measurement", Measurement (Springer), under revision.

■ Cheolhwan Kim, Dongyeob Shin, Bohun Kim, and Jongsun Park, "Mosaic-CNN: A Combined Two-Step Zero Prediction Approach to Trade off Computation Energy and Accuracy in Convolutional Neural Network", IEEE Journal of Emerging and Selected Topics in Circuits and Systems, to be published.

■ Seung-heon Chris Baek, Kyung-Woong Park, Deok-Sin Kil, Yunho Jang, Jongsun Park, Kyung-Jin Lee, and Byong-Guk Park, "Complementary Logic Operation based on Electric-Field Controlled Spin-Orbit Torques", Nature Electronics, to be published.

■ Asmit De, Mohammad Nasim Imtiaz Khan, Jongsun Park, Swaroop Ghosh, "Replacing eFlash with STTRAM in IoTs: Security challenges and Solutions", Journal of Hardware and Systems Security (Springer), to be published.

■ Dongyeob Shin, and Jongsun Park, "A Low-latency and Area-efficient Gram-Schmidt based QRD Architecture for MIMO Receiver", IEEE Transactions on Circuits and Systems I, vol. 65, no. 8, pp. 2606-2616, Aug. 2018.

■ Juseong Lee, Hoyoung Tang, and Jongsun Park, "Energy Efficient Canny Edge Detector for Advanced Mobile Vision Applications", IEEE Transactions on Circuits and Systems for Video Technology, vol. 28, no. 4, pp. 1037-1046, Apr. 2018.

■ Byeonggil Park, Jongsun Park, and Youngjoo Lee, "Area-optimized Fully-flexible BCH Decoder for Multiple GF Dimensions", IEEEAccess, vol. 6, pp. 14498-14509, Mar. 2018.

■ Woong Choi, Kyungrak Choi, and Jongsun Park, "Low Cost Convolutional Neural Network Accelerator Based on Bi-directional Filtering and Bit-width Reduction", IEEE Access, vol. 6, pp. 14734-14746, Mar. 2018.

■ Gyuseong Kang, Woong Choi, and and Jongsun Park, "Embedded DRAM-Based Memory Customization for Low-Cost FFT processor Design", IEEE Transactions on VLSI Systems, vol. 25, no. 12, pp. 3484-3494, Dec. 2017.

■ Dongyeob Shin, Jangwon Park, Jongsun Park, Somnath Paul, and Swarup Bhunia, "Adaptive ECC for Tailored Protection of Nanoscale Memory", IEEE Design & Test, vol. 34, no. 6, pp. 84-93, Dec. 2017.

■ Yong-Seok Lim, Hyunseok Ahn, and Jongsun Park, "Analysis of Antenna Structure for Energy Beamforming in Wireless Power Transfer", IEEE Transactions on Antennas and Propagation, vol. 65, no. 11, pp. 6085-6094, Nov. 2017.

■ Woong Choi, and Jongsun Park, "Improved Perturbation Vector Generation Method for Accurate SRAM Yield Estimation", IEEE Transactions on CAD of Integrated Circuits and Systems, vol. 36, no. 9, pp. 1511-1521, Sep. 2017.

■ Kyungho Shin, Woong Choi, and Jongsun Park, "Half-Select Free and Bit-Line Sharing 9T SRAM for Reliable Supply Voltage Scaling", IEEE Transactions on Circuits and Systems I, vol. 64, no. 8, pp. 2036-2048, Aug. 2017.

■ Byunggi Kang, Ji-Hwan Yoon, and Jongsun Park, "Low-Complexity Massive MIMO Detectors Based on Richardson Method", ETRI Journal, vol. 39, no. 3, pp. 326-335, June 2017.

■ Byeonggil Park, Seungyong An, Jongsun Park, and Youngjoo Lee, "Novel Folded-KES Architecture for High-speed and Area-efficient BCH Decoders", IEEE Transactions on Circuits and Systems II, vol.54, no.5, pp. 535-539, May 2017.

■ Swaroop Ghosh, Anirudh Srikant lyengar, Hamid Reza Motaman, Rekha Govindraj, Jae-won Jang, Jinil Chung, Jongsun Park, Xin Li, Rajiv Joshi, and Denish Somasekhar, "Overview of Circuits, Systems and Applications of Spintronics", IEEE Journal of Emerging and Selected Topics in Circuits and Systems, vol.6, no. 3, pp. 265-278, Sep. 2016.

■ Woong Choi and Jongsun Park, "A Charge-Recycling Assist Technique for Reliable and Low Power SRAM Design", IEEE Transactions on Circuits and Systems I, vol. 63, no. 8, pp. 1164-1175, Aug. 2016.

■ Yunseong Lee, Woojin Jeon, Yeonchoo Cho, Min-Hyun Lee, Seong-Jun Jeong, Jongsun Park, and Seongjun Park, “Mesostructured HfxAlyO2 Thin Films as Reliable and Robust Gate Dielectrics with Tunable Dielectric Constants for High-Performance Graphene-Based Transistors”, ACS Nano, vol. 10, no. 7, pp. 6659-6666, July 2016.

■ Sandip Ray, Jongsun Park, and Swarup Bhunia, "Wearables, Implants, and Internet of Things: The Technology Needs in the Evolving Landscape", IEEE Transactions on Multi-Scale Computing Systems, vol.2, no.2, pp.123-128, April-June 2016.

■ Hoyoung Tang and Jongsun Park, "Unequal-Error-Protection Error Correction Codes (UEEP-ECC) for the Embedded Memories in Digital Signal Processors", IEEE Transactions on VLSI Systems, vol.24, no.6, pp. 2397-2401, June 2016.

■ Chan-Keun Kwon, Hoonki Kim, Jongsun Park, and Soo-Won Kim, "A 0.4-mW, 4.7-ps Resolution Single-Loop sigma-delta TDC Using a Half-Delay Time Integrator", IEEE Transactions on VLSI Systems, vol.24, no.3, pp. 1184-1188, Mar. 2016.

■ Iput Heri Kurniawan, Ji-Hwan Yoon, Jong-Kook Kim, and Jongsun Park, "A Low-Power Channel-Adaptive Reconfigurable 4x4 QRM-MLD MIMO Detector", ETRI Journal, vol.38, no.1, pp. 100-111, Feb. 2016.

■ Jinil Chung, Kenneth Ramclam, Jongsun Park, and Swaroop Ghosh, "Exploiting Serial Access and Asymmetric Read/Write of Domain Wall Memory for Area and Energy-Efficient Digital Signal Processor Design", IEEE Transactions on Circuits and Systems I, vol.63, no.1, pp. 91-102, Jan. 2016.

■ Joon Goo Lee, Seon Wook Kim, Dong-Hyun Kim, Younga Cho, Jae-Sung Rieh, Gyusung Kang, Jongsun Park, Hokyu Lee, Sejin Park, and Chulwoo Kim, "D2ART: Direct Data Accessing from Passive RFID Tag for Infra-less, Contact-less, and Battery-less Pervasive Computing", Microprocessors and Microsystems Journal, vol. 39, no. 8, pp. 767-781, Nov. 2015.

■ Yong-Seok Lim and Jongsun Park, "A Novel Phase Control based Energy Beamforming Techniques in Nonradiative Wireless Power Transfer System", IEEE Transactions on Power Electronics, vol.30, no.11, pp. 6274-6287, Nov. 2015.

■ Woong Choi, Gyuseong Kang, and Jongsun Park, "A Refresh-Less eDRAM Macro With Embedded Voltage Reference and Selective Read for an Area and Power Efficient Viterbi Decoder", IEEE Journal of Solid States Circuits, vol.50, no.10, pp. 2451-2462, Oct. 2015.

■ Ji-Hwan Yoon and Jongsun Park, "An Efficient Memory Address Remapping Technique for High-Throughput QC-LDPC Decoder", Circuits, Systems & Signal Processing (Springer), vol. 33, no. 11, pp. 3457-3473, Nov. 2014.

■ Jong Won Chung, Yeong Hwan Ko, Young Ki Hong, Wongeon Song, Chulseung Jung, Hoyoung Tang, Jiyoul Lee, Min hyung Lee, Bang-lin Lee, Yongwan Jin, Sangyoon Lee, Jaesu Yu, Jongsun Park, and Sunkook Kim, "Flexible Nano-Hybrid Inverter Based on Inkjet-printed Organic and 2D Multilayer MoS2 Thin Film Transistor", Organic Electronics, vol.15, no. 11, pp. 3038-3042, Nov. 2014.

■ Se-Chun Park, You-Sung Kim, Ho-Youb Cho, Sung-Dae Choi, Mi-Sun Yoon, Tae-Yun Kim, Jongsun Park, and Soo-Won Kim, "A Variable Program Cache Busy Time Technique for Reducing Peak Current of NAND Flash Memory in SSD Application", ETRI Journal, vol. 36, no. 5, pp. 876-879, Oct. 2014.

■ Yong-Seok Lim, Hoyoung Tang, Seung-Ok Lim, and Jongsun Park, "An Adaptive Impedance Matching Network Based on a Novel Capacitor-Matrix for Wireless Power Transfer", IEEE Transactions on Power Electronics, vol. 29, no. 8, pp. 4403-4413, Aug. 2014. (2nd place Transaction Paper Award for 2014 in IEEE TPEL)

■ Anandaroop Ghosh, Somnath Paul, Jongsun Park, and Swarup Bhunia, "Improving Energy Efficiency in FPGA through Judicious Mapping of Computation to Embedded Memory Blocks", IEEE Transactions on VLSI Systems, vol. 22, no. 6, pp. 1314-1327, June 2014.

■ Min-Woo Lee, Ji-Hwan Yoon, and Jongsun Park, "A Reconfigurable CORDIC-based Low-Power DCT Architecture Based on Data Priority", IEEE Transactions on VLSI Systems, vol. 22, no. 5, pp. 1060-1068, May 2014.

■ Jangwon Park, Jongsun Park, and Swarup Bhunia, "VL-ECC: Variable Data-Length Error Correction Code for Embedded Memory in DSP Applications", IEEE Transactions on Circuits and Systems II, vol. 61, no. 2, pp. 120-124, Feb. 2014.

■ Insoo Lee, Jinmo Kwon, Jangwon Park, and Jongsun Park, "Priority Based Error Correction Code (ECC) for the embedded SRAM memories in H.264 system", Journal of Signal Processing Systems (Springer), vol. 73, no. 2, pp. 123-136, Nov. 2013.

■ Young-Jae Min, Hoon-Ki Kim, Yu-Ri Kang, Gil-Su Kim, Jongsun Park, and Soo-Won Kim, "Design of Wavelet-Based ECG Detector for Implantable Cardiac Pacemakers", IEEE Transactions on Biomedical Circuits and Systems, vol. 7, no. 4, pp. 426-436, Aug. 2013.

■ Phi-Hung Pham, Junyoung Song, Jongsun Park, and Chulwoo Kim, “Design and Implementation of an On-Chip permutation Network for Multiprocessor System-On-Chip", IEEE Transactions on VLSI Systems, vol. 21, no. 1, pp. 173-177, Jan. 2013.

■ Jinmo Kwon, Ikjoon Chang, Insoo Lee, Heemin Park, and Jongsun Park, "Heterogeneous SRAM Cell Sizing for Low Power H.264 Applications", IEEE Transactions on Circuits and Systems I, vol. 59, no. 10, pp. 2275-2284, Oct. 2012.

■ Woojin Rim, Woong Choi, and Jongsun Park, "Adaptive Clock Generation Technique for Variation-Aware Subthreshold Logics," IEEE Transactions on Circuits and Systems II, vol. 59, no. 9, pp. 587-591, Sep. 2012.

■ Seok Joong Hwang, Youngsun Han, Seon Wook Kim, Jongsun Park, and Byung Gueon Min, "Resource Efficient Implementation of Low Power MB-OFDM PHY Baseband Modem With Highly Parallel Architecture", IEEE Transactions on VLSI Systems, vol. 20, no. 7, pp. 1248-1261, Jul. 2012.

■ Phi-Hung Pham, Jongsun Park, Phuong Mau, and Chulwoo Kim, "Design and Implementation of a Backtracking Wave-pipeline Switch to Support Guaranteed Throughput in Network-on-Chip", IEEE Transactions on VLSI Systems, vol. 20, no. 2, pp. 270-283, Feb. 2012.

■ Seok-Jae Lee, Ji-Woong Choi, Seon Wook Kim, and Jongsun Park, “A Reconfigurable FIR Filter Architecture to Trade off Filter Performance for Dynamic Power Consumption”, IEEE Transactions on VLSI Systems, vol. 19, no. 12, pp. 2221-2228, Dec. 2011.

■ Sunkook Kim, Woong Choi, Woojin Rim, Youngtea Chun, Hongshik Shim, Hyukjun Kwon, Jongsoo Kim, Inseo Kee, Sungchul Kim, Sang Yoon Lee, and Jongsun Park, "A Highly-Sensitive Capacitive Touch Sensor Integrated on a Thin-Film-Encapsulated Active-Matrix OLED for Ultrathin Displays," IEEE Transactions on Electron Devices, vol. 58, no. 10, pp. 3609-3615, Oct. 2011.

■ Doo-Chan Lee, Kyu-Young Kim, Young-Jae Min, Jongsun Park, and Soo-Won Kim, "A Jitter and Power Analysis on DCO," IEEE Transactions on Circuits and Systems II, vol. 58, no. 9, pp. 560-564, Sep. 2011.

■ Kyu-Young Kim, Doo-Chan Lee, Yu-Ri Kang, Soo-Won Kim, and Jongsun Park, “An Energy Efficient Vpp Generator with Fast Ramp-up Time for Mobile DRAM”, IEEE Journal of Solid-State Circuits, vol. 46, no. 6, pp. 1488-1494, June 2011.

■ Kyu-Young Kim, Young-Jae Min, Soo-Won Kim, and Jongsun Park, “Low-power Programmable Divider with a Shared Counter for Frequency Synthesizers”, IET Circuits, Devices & Systems, vol. 5, no. 3, pp. 170-176, May 2011.

■ Min-Woo Lee and Jongsun Park, "Sign-Select Lookahead CORDIC based High-Speed QR Decomposition Architecture for MIMO Receiver Applications",Journal of Semiconductor Technology and Science, vol. 11, no. 1, pp. 6-14, Mar. 2011.

■ Ik Joon Chang, Jongsun Park, Kunhyuk Kang, and Kaushik Roy, “Fast and Accurate Estimation of SRAM Read and Hold Failure Probability using Critical Point Sampling”, IET Circuits, Devices & Systems, vol. 4, no. 6, pp. 469-478, Nov. 2010.

■ Ji-Woong Choi, Jungwon Lee, Byung Gueon Min, and Jongsun Park, “Energy Efficient Hardware Architecture of LU Triangularization for MIMO Receiver”, IEEE Transactions on Circuits and Systems II, vol. 57, no. 8, pp. 632-636, Aug. 2010.

■ Sunkook Kim, Seongmin Kim, Jongsun Park, Sanghyun Ju, and Saeed Mohammadi, “Fully Transparent Pixel Circuits Driven by Random Network Carbon Nanotube Transistor Circuitry”, ACS Nano, vol. 4, no. 6, pp. 2994-2998 Jun. 2010.

■ Jongsun Park, Jung Hwan Choi, and Kaushik Roy, "Dynamic Bit-width Adaptation in DCT: An Approach to Trade off Image Quality and Computation Energy", IEEE Transactions on VLSI Systems, vol 18, no. 5, pp. 787-793, May 2010.

■ Yongtao Wang, Hamid Mahmoodi, Lih-Yih Chiou, Hunsoo Choo, Jongsun Park, Woopyo Jeong and, Kaushik Roy, “Energy-efficient Hardware Architecture and VLSI Implementation of a Polyphase Channelizer with Applications to Subband Adaptive Filtering”, Journal of Signal Processing Systems, vol. 58, no. 2, pp. 125-137, Feb. 2010.

■ Jungwon Lee, Ji-Woong Choi, Hui-Ling Lou, and Jongsun Park, “Soft MIMO ML Demodulation Based on Bitwise Constellation Partitioning”, IEEE Communications Letters, vol. 13, no. 10, pp. 736-738, Oct. 2009.

■ Jin-Woo Kim, Kyeong Hur, Jongsun Park, and Doo-Seop Eom "A distributed MAC design for data collision-free wireless USB home networks", IEEE Transactions on Consumer Electronics, vol. 55, no. 3, pp. 1337-1343, Aug. 2009.

■ Seok-Hwan Kim, Kyeong Hur, Jongsun Park, Doo-Seop Eom, and Kwang-il Hwang, "A Fair Distributed Resource Allocation Method in UWB Wireless PANs with WiMedia MAC" Journal of Communications and Networks, vol. 11, no. 4, pp. 375-383, Aug. 2009.

■ Seung Beom Lee, Kyeong Hur, Jongsun Park, and Doo-Seop Eom, "A packet forwarding controller for mobile IP-based networks with packet buffering", IEEE Transactions on Consumer Electronics, vol. 55, no. 3, pp 1344-1350, Aug. 2009.

■ Jongsun Park and Kaushik Roy, "Low Complexity Reconfigurable DCT Architecture to Trade off Image Quality for Power Consumption", Journal of Signal Processing Systems, vol. 53, no. 3, pp. 399-410, Dec. 2008.

■ Jongsun Park, Khurram Muhammad, and Kaushik Roy, "Efficient Modeling of 1/fα Noise Using Multirate Process", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 25, no. 7, pp. 1247-1256, Jul. 2006.

■ Jongsun Park, Woopyo Jeong, Hamid Mahmoodi, Yongtao Wang, Hunsoo Choo, and Kaushik Roy, "Computation Sharing Programmable FIR Filter for High Performance and Low Power Applications", IEEE Journal of Solid States Circuits, vol. 39, no. 2, pp. 348-357, Feb. 2004.

■ Jongsun Park, Khurram Muhammad, and Kaushik Roy, "High Performance FIR Filter Design Based on Sharing Multiplication", IEEE Transactions on VLSI Systems, vol. 11, no. 2, pp. 244-253, Apr. 2003.

Selected Conference Publications

■ Gyuseong Kang, Yunho Jang, and Jongsun Park, "Spin Orbit Torque Device based Stochastic Multi-bit Synapses for On-chip STDP learning", International Symposium of Low Power Electronics and Applications (ISLPED), July 2018.

■ Heetak Kim and Jongsun Park, "Designing Energy Efficient High Accuracy Spiking Neural Network using Approximate Computing", 2018 SoC 학술대회, May 2018.

■ Woong Choi, Hoonki Kim, Changnam Park, Taejoong Song and Jongsun Park, "Half-and-Half Compare Content Addressable Memory with Charge-Sharing based Selective Match-Line Precharge Scheme", IEEE Symposium on VLSI Circuits (VLSIC), June 2018.

■ Hoyoung Tang, Heetak Kim, Donghyeon cho and Jongsun Park, "Spike Counts Based Low Complexity Learning with Binary Synapse", International Joint Conference on Neural Networks (IJCNN), July 2018.

■ Woong Choi, Kwanghyo Jeong, Kyungrak Choi, Kyeongho Lee and Jongsun Park, "Content Addressable Memory Based Binarized Neural Network Accelerator Using Time-Domain Signal Processing", Design Automation Conference (DAC), Jun. 2018.

■ Woong Choi, Kyeongho Lee and Jongsun Park, "Low Cost Ternary Content Addressable Memory Using Adaptive Matchline Discharging Scheme", IEEE International Symposium on Circuits and Systems (ISCAS), May 2018.

■ Gyuseong Kang, Yunho Jang and Jongsun Park, "Charge-Recycling based Redundant Write Prevention Technique for Low Power SOT-MRAM", IEEE International Symposium on Circuits and Systems (ISCAS), May 2018.

■ Nahsung Kim, Dongyeob Shin, Wonseok Choi, Bohun Kim, and Jongsun Park, "An Energy-efficient and Low area CNN Accelerator based on Combined Weight Type Quantization", 한국반도체학술대회, Feb. 2018.

■ Donghyeon Cho, Gyuseong Kang, Heetak Kim, Yunho Jang, and Jongsun Park, "Energy efficient Spike-Timing Dependent Plasticity Rule for Unsupervised Learning", 한국반도체학술대회, Feb. 2018.

■ Kwanghyo Jeong, Kyeongho Lee, Woong Choi, and Jongsun Park, "Low Power Contents Addressable Memory with NMOS Gated Selective Precharge Matchline", 한국반도체학술대회, Feb. 2018.

■ Wonseok Choi and Jongsun Park, "An Efficient Convolutional Neural Networks Design with Heterogeneous SRAM Cell Sizing", IEEE ISOCC, Nov. 2017.

■ Kyungrak Choi, Woong Choi, Kyungho Shin, and Jongsun Park, "Bit-width Reduction and Customized Register for Low Cost Convolutional Neural Network Accelerator", International Symposium on Low Power Electronics (ISLPED), July 2017.

■ Qianying Tang, Chen Zhou, Woong Choi, Gyuseong Kang, Jongsun Park, Keshab Parhi, and Chris H. Kim, "A DRAM based Physical Unclonable Function Capable of Generating > 1032 Challenge Response Pair per 1Kbit Array for Secure Chip Authentication", Custom Integrated Circuits Conference (CICC), Apr. 2017.

■ Cheolhwan Kim, Gyuseong Kang and Jongsun Park, "Approximate Computation Sharing Multiplier for Low Power Convolutional Neural Networks Design", 한국반도체학술대회, Feb. 2017.

■ Sangkyu Lee, Hoyoung Tang, Kyungrak Choi, and Jongsun Park, "Customized SRAM design for Low Power Video codec applications", IEEE ISOCC, Oct. 2016.

■ Gihoon Jung, Kyungrak Choi, and Jongsun Park, "A Compact Multi-Mode CORDIC with Global-Shifting-Sum (GSS) Method", IEEE Asia Pacific Conference on Circuits & Systems (APCCAS), Oct. 2016.

■ Jinil Chung, Jongsun Park, and Swaroop Ghosh, "Domain Wall Memory based Convolutional Neural Networks for Bit-width Extendability and Energy-Efficiency", International Symposium on Low Power Electronics (ISLPED), Aug. 2016.

■ Kyungrak Choi, Jinil Chung, Hoyoung Tang, Woong Choi, and Jongsun Park, "Low Power Embedded SRAM for Pipelined Bitonic Sorter", 2016 대한전자공학회 하계종합학술대회, Jun. 2016.

■ Cheolhwan Kim, Byeongil Park, Gyuseong Kang, and Jongsun Park, "Retention-aware Reconfigurable eDRAM-based LIFO Memory Design for DSP System", 2016 대한전자공학회 하계종합학술대회, Jun. 2016.

■ Kyungrak Choi, Hoyoung Tang, Woong Choi, and Jongsun Park, "Low Power SRAM for FFT Processor with preventing unnecessary Pseudo-Read and Wordline activation", 2016 SoC 학술대회, May. 2016.

■ Byeonggil Park, Gyuseong Kang, and Jongsun Park, "Retention-Time Aware Reconfigurable eDRAM-based FIFO Memory for Refresh-Free DSP Design", 한국반도체학술대회, Feb. 2016.

■ Dongyeob Shin, Ji-Hwan Yoon, Gihoon Jung, and Jongsun Park, "A Low Complexity Massive MIMO Detection Architecture based on Richardson Iterative Method", 한국반도체학술대회, Feb. 2016.

■ Woong Choi, Kyungho Shin, and Jongsun Park, "Unnecessary Pseudo-Read Prevent SRAM for Low-Power Viterbi Decoder", 한국반도체학술대회, Feb. 2016.

■ Kyungho Shin and Jongsun Park, "A Single-Ended 6T1D SRAM Cell With Feedback-fade Write Access for Near-threshold Operation", 2015 추계학술대회.

■ Seungyong An, Hoyoung Tang, and Jongsun Park, "A Inversion-Less Peterson algorithm based shared KES architecture for Concatenated BCH decoder", IEEE ISOCC, Nov. 2015.

■ Byunggi Kang and Jongsun Park, "Low Complexity Massive MIMO Detection Architecture based on Neumann Method", IEEE ISOCC, Nov. 2015.

■ Jinil Chung, Kenneth Ramclam, Swaroop Ghosh, and Jongsun Park, “Domain Wall Memory based Digital Signal Processors for Area and Energy-Efficiency”, Design Automation Conference (DAC), June 2015.

■ Jae-Won Jang, Jongsun Park, Swaroop Ghosh, and Swarup Bhunia, “Self-Correcting STTRAM under Magnetic Field Attacks”,Design Automation Conference (DAC), June 2015.

■ Hoyoung Tang, Gihoon Jung, and Jongsun Park "A Hybrid Multimode BCH Encoder Architecture for Area Efficient Re-Encoding Approach", IEEE ISCAS, May. 2015.

■ Gihoon Jung and Jongsun Park " An Area Efficient Scaling-Free CORDIC Algorithm Using Global Shifting Sum(GSS) Method", 한국반도체학술대회, Feb. 2015.

■ Hoyoung Tang and Jongsun Park "A MP-based BCH Encoder for Reducing the Latency of SC based on re-Encoding Architecture", 한국반도체학술대회, Feb. 2015.

■ Gyuseong Kang and Jongsun Park " Low Power Signal Processing Unit for Pulse Oximetry", 한국반도체학술대회, Feb. 2015.

■ Woong Choi, Jongsun Park, and Gyuseong Kang "Dynamic Stability Estimation for Latch-Type Voltage Sense Amplifier", IEEE ISOCC, Nov. 2014.

■ Dongyeob Shin, Ji-Hwan Yoon, Jongsun Park, and Woong Choi "Gram-Schmidt tailed High-throughput QR Decomposition Architecture for MIMO detector", IEEE ISOCC, Nov. 2014.

■ Ji-Hwan Yoon, Dongyeob Shin, and Jongsun Park, "A Low-Complexity Composite QR Decomposition Architecture for MIMO Detector", IEEE ISCAS, June 2014.

■ Jinil Chung and Jongsun Park, "Unified Single-port Survivor Memory for High-speed Viterbi Decoder using 3-unit Packing/Unpacking-based Data Processing", 한국반도체학술대회, Feb. 2014.

■ Juseong Lee and Jongsun Park, "Hardware Optimization for Low Complexity Edge Detection", 한국반도체학술대회, Feb. 2014.

■ Abhishek Basak, Yu Zheng, Jangwon Park, Jongsun Park, and Swarup Bhunia, "Reconfigurable ECC for Adaptive Protection of Memory", IEEE MWSCAS, August 2013.

■ 송동후, 이주성, 신동엽, 박종선, "Heterogeneous Precharge Level을 이용한저전력 H.264용 임베디드 SRAM 설계", 2013 대한전자공학회 하계종합학술대회.

■ Iput Heri Kurniawan, Ji-Hwan Yoon, and Jongsun Park, "Multidimensional Householder based High-Speed QR Decomposition Architecture For MIMO Receivers", IEEE ISCAS, May 2013.

■ 당호영, 송동후, 신동엽, 박종선, "Write 동작의 에너지 감소를 통한 Viterbi decoder전용 저전력 임베디드 SRAM 설계", 2013SoC 학술대회.

■ Samir Debnath, Woong Choi, and Jongsun Park, "A Single-Ended 6T SRAM Cell with Read-Upset-Preventor", 2012 추계학술대회.

■ Dongwan Kim, Wan-Seon Lim, and Jongsun Park, "Dual Queue based Rate Selecting Schedule for Throughput Enhancement in WLANs", IEEE ISCAS, pp. 540-543, May 2012.

■ Min-Woo Lee, Ji-Hwan Yoon, and Jongsun Park, "High-Speed Tournament Givens Rotation-based QR Decomposition Architecture for MIMO reciever", IEEE ISCAS, pp. 21-24, May 2012.

■ 이민우, 박종선, “Low Power CORDIC Architecture Using Trigonometric Characteristics”, pp.365-366, 2012 반도체 학술대회.

■ 박장원, 권진모, 김동완, 박종선, “저전력 H.264 프로세서를 위한 가변적인 비트 폭임베디드 메모리 설계”, pp. 302-303, 2012 반도체 학술대회.

■ 윤지환, 박종선, “알고리즘적인 재공식화를 통한 저전력 LDPC 복호기의 설계”, 2011 추계학술대회.

■ Woojin Rim, Jinmo Kwon, and Jongsun Park, "Variation-aware low-power video processor design techniques", IEEE MWSCAS,2011.

■ Ji-Woong Choi, Jungwon Lee, Hui-Ling Lou, and Jongsun Park, "Improved MIMO SIC Detection Exploiting ML Criterion", IEEE VTC, Fall, 2011.

■ 권진모, 박종선, “저전력 H.264 프로세서를 위한 이종 사이즈 임베디드 메모리설계”, 2011 SoC 학술대회.

■ 이인수, 박종선, “저전력 H.264/AVC의 어플리케이션을 위한 중요도 기반 에러 보정부호화 방안”, 2010 추계학술대회.

■ 이석재, 이민우, 최지웅, 박종선, “An Energy-Efficient Reconfigurable DLMS Adaptive Filter Design”, 2010 SoC 학술대회.

■ Seetharam Narasimhan, Jongsun Park, and Swarup Bhunia, “Digital Signal Processing in Bio-implantable Systems: Design Challenge and Emerging solutions”, ASQED, 2010.

■ 이민우, 박종선, “High Performance CORDIC Architecture using Sign-Select Lookahead Approach”, 제17회 한국반도체학술대회,2010.

■ Jongsun Park, Jung Hwan Choi, and Kaushik Roy,"Dynamic Bit Width Adaptation in DCT : Image Quality versus Computation Energy Trade off", DATE, 2006.

■ Yongtao Wang, Hamid Mahmoodi, Hunsoo Choo, Jongsun Park, Woopyo Jeong, Lihyih Chiou and Kaushik Roy, "Hardware Architecture and VLSI Implementation of a low-power high-performance polyphase channelizer with application to subband adaptive filtering", IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Volume 5, pp 97-100, May, 2004.

■ Jongsun Park and Kaushik Roy,"A low power reconfigurable DCT architecture to trade off image quality for computational complexity", IEEE ICASSP, May 2004.

■ Jongsun Park, Khurram Muhammad and Kaushik Roy, "Efficient Generation of 1/fα Noise Using a Multi-rate Filter Bank", IEEE Custom Integrated Circuit Conference (CICC), pp 707-710, September, 2003.

■ Jongsun Park, Woopyo Jeong, Hunsoo Choo, Hamid Mahmoodi, Yongtao Wang, Kaushik Roy, "High performance and Low power FIR filter Design Based on Sharing Multiplication", IEEE International Symposium on Low Power Electronics Design (ISLPED), pp 295-300, August, 2002.

■ Soonkeon Kwon, Jongsun Park and Kaushik Roy, "DCT Processor Architecture Based on Computation Sharing", IEEE International Conference on Circuits and Systems for Communications, pp 162-165, June, 2002.

■ Jongsun Park, Soonkeon Kwon, Kaushik Roy "Low Power Reconfigurable DCT Design based on Sharing Multiplication", IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Vol.3, pp.3116-3119, June, 2002.

■ Jongsun Park, Hunsoo Choo, Khurram Muhammad, Kaushik Roy "Non adaptive and Adaptive Filter implementation based on sharing multiplication", IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Volume 1, pp 460-463, June 2000.

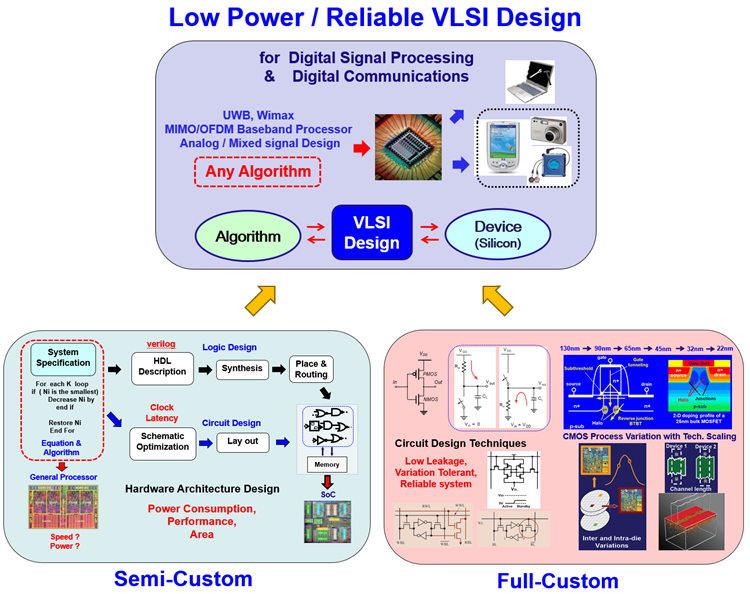

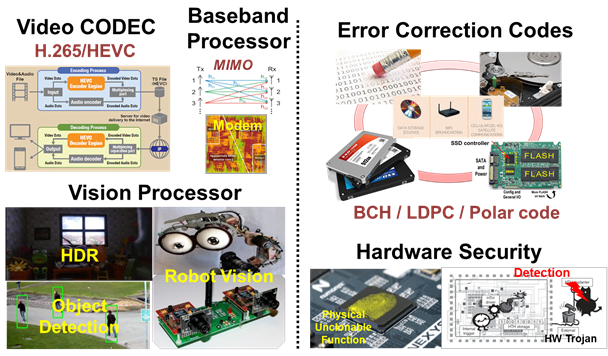

Research

Research Topic

Our research interests range from classical low power reliable VLSI design to recent/emerging digital system development. The applications encompass various neural network (CNN, RNN, SNN, DNN) accelerators, embedded memories for mobile and IoT applications, and application-specific processors for communications, image processing, and security hardware.

Design Flow

Neural Networks

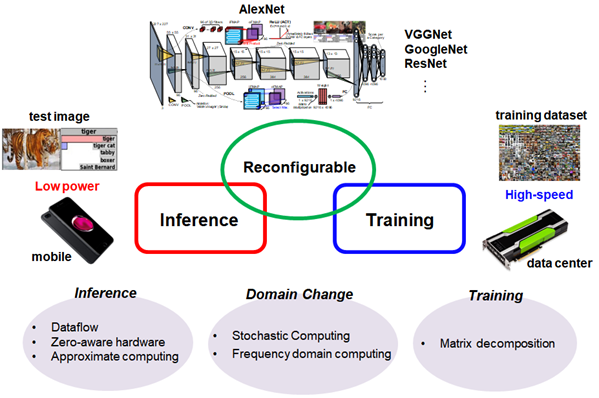

Convolutional Neural Network(CNN)

Convolutional neural network (CNN) is one of the most widely used neural network models for image pattern recognition. The latest CNN models have better performance than humans, but they require a lot of computational complexity and huge data storage space. Due to its large input datasets and weight parameters for convolution operations, a high-speed and low-power(energy) ASIC design to accelerate CNN operations becomes very important. Our research focus is a CNN accelerator design for energy efficient inference/training of various CNN models by applying the following techniques.

- Dataflow which maximizes throughput per energy consumption

- Zero-aware hardware architecture (zero weight from pruning-training, zero input from ReLU-inference)

- Approximate computing techniques for low power consumption

- Various implementation techniques based on domain change

- Training architecture optimization

- Reconfigurable CNN accelerator which can adapt to various CNN specifications

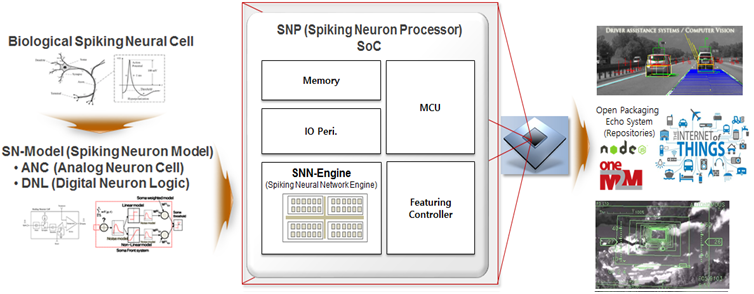

Spiking Neural Network(SNN)

Spiking neural network (SNN) is a brain-inspired network to realize neuromorphic system. The focus of our current research isdeveloping the area efficient spiking neural model and accurate learning method for the SNN. Also implementation of the SNN is our another research focus to enable low power consumption and energy efficient computation for wide range of tasks. The followings are research topics:

- Preprocessing method for improving the accuracy of computation

- Learning method for synaptic weights of the spiking neuron network

- Hardware efficient SNN architecture

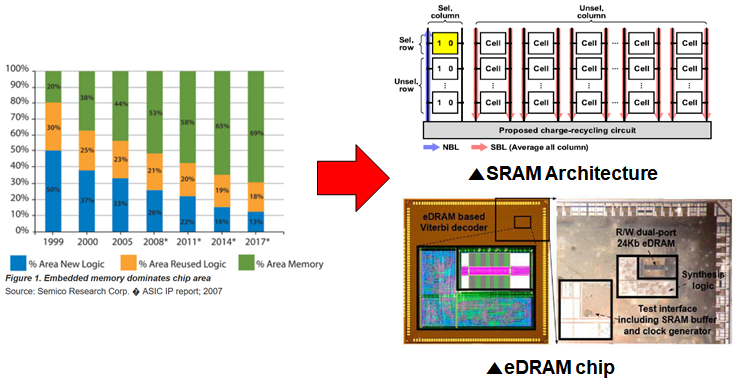

Embedded Memories

SRAM & eDRAM

Embedded memory for IoT occupies a large area on the chip, and it affects the performance of the entire chip. Therefore, it is important to design a low-area, low-power, high-performance memory. In addition, due to the shrinking of process technology, the importance of reliability at low voltage becomes an issue. So, we focus on embedded memory design using SRAM and eDRAM, and we are studying memory performance improvement and memory design optimized for various applications.

The followings are the areas of research we are currently interested in.

- SRAM cell design

- SRAM Peripheral Circuit design

- SRAM Yield Estimation modeling

- Application specific Memory using eDRAM

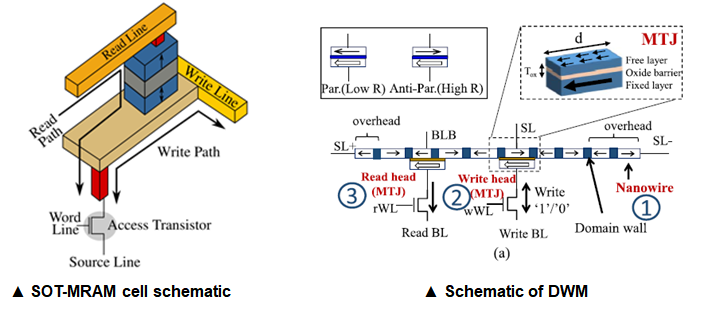

Emerging Memories

CMOS based memories, such as SRAM leads to static power consumption which disturb scaling of device. Several non-volatile memory (NVM) technologies, such as spin-orbit torque MRAM (SOT-MRAM), domain wall memory (DWM) have emerged as possible candidates to substitute or assist SRAM. The focus of our current research

- Circuit design of New Memory for low power consumption, high reliability and fast operation

- Memory customization for low power, better performance.

Digital Signal Processors

- Efficient interface design of embedded memory (SRAM) for low power MPEG/H.264 applications

- Low-power MIMO/OFDM baseband processor design

- Design of robot vision processor for supporting multiple camera operations

- Low power image processing design for advanced mobile vision applications

- VLSI implementation of error correction codes (ECC) for high speed PCRAM/DRAM interfaces

- Memory based computation of cryptography processor and physical unclonable function (PUF)

Teaching

Class Awards

n 2017 Spring - Seok Top Teaching Award

n 2013 Fall - Seok Top Teaching Award

n 2012 Spring - Seok Top Teaching Award

n 2011 Fall - Seok Top Teaching Award

n 2011 Spring - Seok Top Teaching Award

n 2010 Spring - Seok Top Teaching Award

n 2009 Spring - Seok Top Teaching Award

Undergraduate Classes

n 2017 Fall - KECE496 Digital Integrated Circuits (English Class)

n 2017 Spring - KECE463 VLSI Design and Implementations (English Class)

n 2017 Spring - KECE303 Electronic Circuit Design and Experiment I

n 2017 Spring - KEEE301 Electronic Circuits I (English Class)

n 2016 Fall - KECE496 Digital Integrated Circuits (English Class)

n 2016 Spring - KECE463 VLSI Design and Implementations (English Class)

n 2016 Spring - KECE303 Electronic Circuit Design and Experiment I (English)

n 2016 Spring - KECE301 Electronic Circuits I (English Class)

n 2015 Fall - KECE496 Digital Integrated Circuits (English Class)

n 2015 Fall - KECE404 Graduation Project II

n 2015 Spring - KECE463 VLSI Design and Implementations (English Class)

n 2015 Spring - KECE401 Graduation Project I

n 2013 Fall - KECE496 Digital Integrated Circuits (English Class)

n 2013 Fall - KECE210 Digital System LAB

n 2013 Spring - KECE463 VLSI Design and Implementations (English Class)

n 2013 Spring - KEEE301 Electronic Circuits I (English Class)

n 2012 Fall - KECE496 Digital Integrated Circuits (English Class)

n 2012 Spring - KECE463 VLSI Design and Implementations (English Class)

n 2012 Spring - KECE303 Electronic Circuits and Laboratory I

n 2012 Spring - KECE301 Electronic Circuits I (English Class)

n 2012 Spring - KECE401 Graduation Project

n 2011 Fall - KEEE464 Digital Integrated Circuits (English Class)

n 2011 Spring - KEEE301 Electronic Circuits I (English Class)

n 2010 Fall - KEEE482 ASIC Design (English Class)

n 2010 Spring - KEEE485 VLSI Design and Implementations (English Class)

n 2010 Spring - KEEE209 Digital System Design and Laboratory (English)

n 2009 Fall - KEEE482 ASIC Design (English Class)

n 2009 Spring - KEEE485 VLSI Design and Implementations (English Class)

n 2009 Spring - KEEE303 Electronic Circuits and Laboratory I (English)

n 2009 Spring - KEEE301 Electronic Circuits I (English Class)

n 2008 Fall - KEEE464 Digital Integrated Circuits (English Class)

n 2008 Spring - KEEE301 Electronic Circuits I (English Class)

n 2008 Spring - KEEE303 Electronic Circuits and Laboratory I (English)

n 2008 Spring - KEEE485 VLSI Design and Implementations (English Class)

Graduate Classes

n 2017 Fall - ECE678 VLSI Signal Processing Systems (English Class)

n 2016 Fall - ECE689 Low Power System Design (English Class)

n 2015 Fall - ECE678 VLSI Signal Processing Systems (English Class)

n 2015 Spring - ECE689 Low Power System Design (English Class)

n 2015 Spring - ITH512 ASIC Design

n 2013 Fall - NSE602 VLSI Signal Processing Systems (English Class)

n 2012 Fall - ECE689 Low Power System Design (English Class)

n 2011 Fall - NSE602 VLSI Signal Processing Systems (English Class)

n 2011 Spring - EKE604 Low Power System Design (English Class)

n 2011 Spring - ITH512 ASIC Design

n 2010 Fall - EKE606 Advanced VLSI Signal Processing Systems (English Class)

n 2010 Spring - EKE604 Low Power System Design (English Class)

n 2009 Fall - NSE602 VLSI Signal Processing Systems (English Class)

n 2009 Spring - ITH512 ASIC Design

n 2008 Fall - EKE604 Low Power System Design (English Class)

Lab Members

Jihwan Yoon (Ph. D. Candidate)

improma

Research Field

MIMO Detector, QR Decomposition Design (MIMO Group)

Hoyoung Tang (Ph. D. Candidate)

ho-2604

Research Field

Error Correction Code Design

Energy Efficient Spiking Neural Network Design (SNN Group Chair)

Gyuseong Kang (Ph. D. Candidate)

ntmouse

Research Field

eDRAM, SOT-MRAM Design (Emerging Memory Group Chair)

Jinil Chung (Ph. D. Candidate)

jinil_chung

Research Field

Domain Wall Memory, Neural Network Hardware Design (CNN Group)

Experience

2004~Present DRAM Design Team, SK Hynix

Dongyeob Shin (Ph. D. Candidate)

shindy919

Research Field

Error Correction Code, QR Decomposition,

Neural Network Hardware Design (CNN Group Chair)

Sangkyu Lee (Ph. D. Candidate)

sangkyu2.lee

Research Field

Error Correction Code Design (ECC Group)

Experience

2004~Present Flash Design Team, SK Hynix

Bohun Kim (Ph. D. Student)

rlaqhgns0616

Research Field

Light-weight Security Module Design (Security Group Chair)

Neural Network Hardware Design (CNN Group)

Yunho Jang (Ph. D. Student)

yunho3469

Research Field

Embedded Memory (SRAM, SOT-MRAM) Design (Emerging Memory Group)

Kyeongho Lee (Ph. D. Student)

rudgh0143

Research Field

Low Power SRAM, CAM Design (Full-custom Group Chair)

Byungjun Choi (Master Student)

bjchoi

Research Field

Light-weight Security Module Design (Security Group)

Junghoon Cho (Ph. D. Student)

twister333

Research Field

Neural Network Hardware Design (CNN Group)

Taehwan Kim (Ph. D. Student)

toto9900

Research Field

Embedded Memory (SRAM, SOT-MRAM) Design (Full-custom Group, Emerging Memory Group)

Energy Efficient Spiking Neural Network Design (SNN Group)

Wonseok Choi (Master Student)

sicnarf

Research Field

Neural Network Hardware Design (CNN Group)

Kwanghyo Jeong (Master Student)

light1510

Research Field

Binarized Neural Network Hardware Design (CNN Group)

Nahsung Kim (Master Student)

arianshidh

Research Field

Neural Network Hardware Design (CNN Group)

Donghyeon Cho (Master Student)

donghyeon_cho

Research Field

Energy Efficient Spiking Neural Network Design (SNN Group)

Heetak Kim (Master Student)

ayddong

Research Field

Energy Efficient Spiking Neural Network Design (SNN Group)

Geon Ko (Master Student)

zepylis

Research Field

Embedded Memory (SRAM, SOT-MRAM) Design (Full-custom Group, Emerging Memory Group)

Daehan Ji (Master Student)

nothingness

Research Field

Neural Network Hardware Design (CNN Group)

Hyeonseong Kim (Master Student)

syzk951

Research Field

Energy Efficient Spiking Neural Network Design (SNN Group)

Alumni

Lee Seok-Jae (Master)

Current Affiliation: Samsung Electronics Memory Division

seokjae1.lee

Thesis Topic

Ultra Low Power DSP Processing

Insoo Lee (Master)

Current Affiliation: Hynix Semiconductor

insoo1.lee

Thesis Topic

Error Correction Code (ECC), Low Power Image Processing

Jinmo Kwon (Master)

Current Affiliation : LG Electronics CTO

jinmo.kwon

Thesis Topic

SRAM, Low Power Image Processing

Min-Woo Lee (Master)

Current Affiliation : LG Electronics CTO

sgsmw

Thesis Topic

CORDIC Based Digital Signal Processing Unit Design

Jangwon Park (Master)

Current Affiliation: Samsung Electronics

jw456461

Thesis Topic

Reconfigurable Error Correction Code

Iput Heri Kurniawan (Master)

Current Affiliation: Raon-tech

iput_kurniawan

Thesis Topic

High Performance MIMO Detector

Debnath Samir(Master)

samir

Thesis Topic

Low Power SRAM

Juseong Lee (Master)

Current Affiliation : Korea Institute of Science and Technology (KIST)

juseong_lee

Thesis Topic

Low Power Image Processing

Seungyong An (Master)

Current Affiliation: Samsung Electronics Memory Division

seungyong

Thesis Topic

Error Correction Coding Design

Gihoon Jung (Master)

Current Affiliation: Agency for Defense Development (ADD)

ghjung

Thesis Topic

Arithmetic Circuit, CORDIC Design

Byunggi Kang (Master)

Current Affiliation: Samsung Electronics Moblie Communication Division

byunggi.kang

Thesis Topic

MIMO Detector Design

Yunseong Lee (Master)

Current Affiliation: Samsung Advanced Institute of Technology (SAIT)

heny4

Thesis Topic

Graphene-based Transistors

Yongseok Lim (Ph. D.)

Current Affiliation: Korea Electronics Technology Institute(KETI)

busytom at keti.re.kr

Thesis Topic

Wireless Power Transfer

Kyungho Shin (Master)

Current Affiliation: Hynix Semiconductor

zzeusz1946

Thesis Topic

Low-power SRAM Design

Byeonggil Park (Master)

Current Affiliation: Samsung Electronics

pbg3000

Thesis Topic

Error Correction Code Design

Woong Choi (Ph.D.)

Current Affiliation: Samsung Electronics

woongchoi84

Thesis Topic

Ultra Low power SRAM and eDRAM Design

Kyungrak Choi (Master)

2010171011

Thesis Topic

Neural Network Hardware Design

Cheolhwan Kim (Master)Current Affiliation: Samsung Electronics

kch9258

Thesis Topic

Neural Network Hardware Design

Yeongkyo Seo (Undergraduate Researcher)

Current Affiliation: Purdue University

syg3434